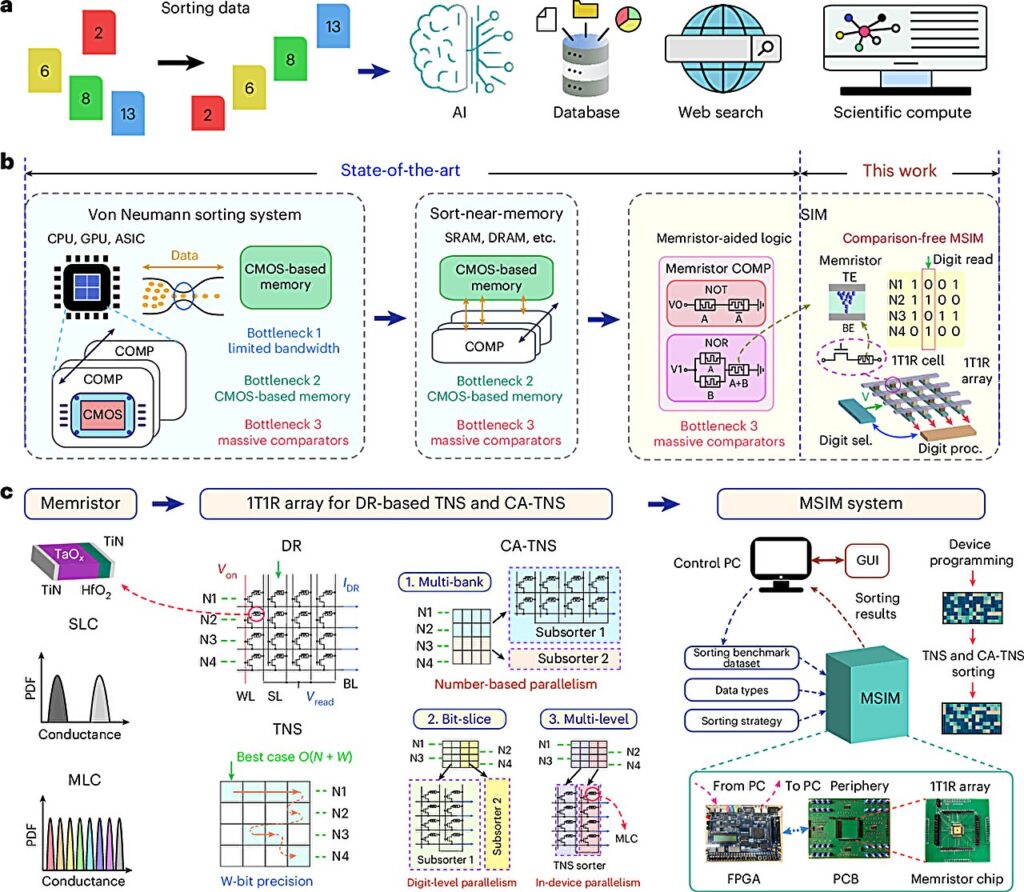

An overview of the sorting system. Credit: Nature Electronics (2025). doi:10.1038/s41928-025-01405-2

The research team, led by Professor Yang Yuchao of the Department of Electronics and Computer Engineering at Peking University Shenzhen Graduate School, achieved a global breakthrough by developing the first memory hardware system tailored to complex, nonlinear sorting tasks.

The study, published in Nature Electronics, is entitled “Fast and Reconfigurable Memory System System Based on Memristors,” proposes an architecture that does not compare and overcomes one of the toughest challenges in the field of memory (PIM) technology.

Sorting is a fundamental computing task, but its nonlinearity makes it difficult to accelerate using traditional hardware. Memristor-based PIM architectures show the potential for linear operations, but they have struggled with sorting for a long time. Professor Yang’s team addressed this by eliminating the need for comparators and introducing a new digit reading mechanism.

This work represents a significant advance in the evolution of PIM technology, from linear matrix operations to nonlinear, high multiple tasks such as sorting. By proposing a scalable and reconfigurable sorting framework, the team provides high-throughput, energy-efficient solutions that meet the performance demands of modern big data and AI applications.

This study presents a comparator-free sorting system built on a single transistor (1T1R) memorist array using digit read mechanisms that replace traditional comparative solution selection logic and greatly improve computational efficiency. The team also developed the Tree Node Skipping (TNS) algorithm. This speeds up sorting by reusing traversal paths to reduce unnecessary operations.

Three cross-array TNS (CA-TNS) strategies have been introduced to expand the performance of diverse datasets and overall configurations. Multibank strategies partition large datasets across an array for parallel processing. Bitslices distribute bit widths and enable pipeline sorting. Multilevels leverage the multiconductance state of the memorist to enhance intracellular parallelism.

Together, these innovations form a flexible and adaptable sort accelerator that can handle a wide range of data widths and complexities.

In-memory sorting is compatible with existing matrix-based in-memory computing, allowing real-time adaptive sparse AI calculations. Credit: Nature Electronics (2025). doi:10.1038/s41928-025-01405-2

To verify real-world performance, the team manufactured memorized chips and integrated them with FPGA and PCB hardware to build a complete end-to-end demo system. Benchmark tests provided up to 7.70x speeds, higher energy efficiency than 160.4x, and 32.46x area efficiency compared to the main ASIC-based sorting systems.

This system has proven effective in real-world applications as well. The Dijkstra path plan successfully calculated the shortest path between 16 Beijing Metro Stations with delays and power consumption. Neural Network Inference enabled tunable sparse in the runtime by integrating TNS with Memristor-based Matrix-Vector multiplication in the Point Net++ model, achieving 15x speed and 67.1x energy efficiency improvements. These results highlight the broad applicability of systems in both traditional and AI-driven workloads.

This task redefines what is possible in memory system processing. By demonstrating a flexible, efficient and scalable screening system, Yang’s team has opened the door to next-generation intelligent hardware that can power AI, real-time analytics, and edge computing. This lays the foundation for future nonlinear computational acceleration and pushes the boundaries of what memorister-based systems can achieve.

Details: A fast and reconfigurable sort-in memory system based on Lianfeng Yu et al, Memristors, Nature Electronics (2025). doi:10.1038/s41928-025-01405-2

Provided by Peking University

Citation: Memory Sorting Hardware System eliminates the need for comparators for nonlinear sorting tasks (2025, July 16) obtained from https://techxplore.com/news/2025-07-memory-hardware-noninear-tasks.html from July 16, 2025.

This document is subject to copyright. Apart from fair transactions for private research or research purposes, there is no part that is reproduced without written permission. Content is provided with information only.